电子工程圈,有一个常被提及的“隐性共识”:电源是产品的瓶颈。

无论是手机、笔记本、电视,还是工控与IoT设备,用户并不会直接谈论电源,但他们的体验却与电源性能息息相关。充电速度够不够快?适配器能不能小一点?待机功耗能不能更低?这些问题的背后,最终都落在电源架构上。

进入2025年,电源产业迎来新的临界点:标准更严苛,需求更苛刻,成本更紧张。对于工程师而言,继续依赖十多年前的QR flyback已经难以为继。于是,GaN与集成化方案则开始成为新的必然选择。

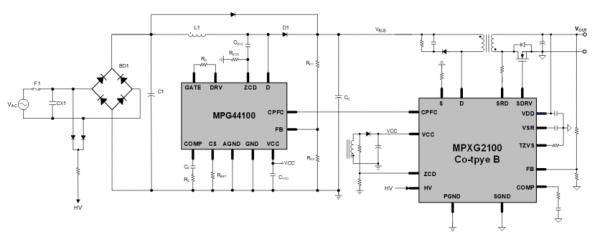

MPS在9月发布的ACDC创新方案,正是在这一背景下推出的。这一次,MPXG2100(NovoOne 系列)与MPG44100,构成了面向20W~200W区间的“双子星组合”,以高的效率、更小的体积、更低的功耗,来回应这场转型。

电源设计的“三重枷锁”:法规、需求与现实的博弈

能源效率标准始终是驱动电源技术革新的“指挥棒”。近年来,中国、欧美等主要市场相继收紧了能效门槛,为行业划定了红线。在中国新国标GB20943-2025中,要求20V/45W的典型档位,平均效率必须达到91.1%;待机功耗被严格限制在50mW以下;轻载效率也被首次纳入考核。

如果说政策层面是“推手”,那么消费者的使用习惯则是市场需求的“拉力”。前几年,一个65W的快充头有“烟盒”大小;而今,用户期望一个140W的笔记本适配器能做到“卡片尺寸”,轻松放入口袋随身携带。

这种对极致便携性的追求,给工程师带来了连锁挑战:要想缩小变压器等磁性元件的体积,唯一的途径就是大幅提高开关频率;但体积减半而功率翻倍,导致热量高度集中,热管理难度呈指数级上升。

同时,开关频率的飙升不可避免地会带来更强的电磁干扰,需要更复杂、更精密的滤波电路来抑制。在这一系列高压要求下,依赖传统硅基MOSFET的架构已“力不从心”,以氮化镓(GaN)、碳化硅(SiC)为代表的第三代半导体,已从“可选项”变为突破瓶颈的必然选择。

除了外部压力,电源设计本身也面临着一个结构性的矛盾,尤其体现在行业最核心的功率区间。在20W以下的低功率段,简单的反激架构凭借其成本优势依然适用;在300W以上的高功率段,LLC等谐振拓扑技术成熟,地位稳固。

然而,在75W至240W之间,恰恰形成了一个“技术真空地带”。反激架构在功率上探至百瓦以上时,效率和散热问题便会凸显;而LLC架构虽然高效,但其对宽电压范围输出的适应性较差,难以满足现代消费电子的动态需求。

而更尴尬的是,手机快充、平板电脑、笔记本、显示器等主流产品几乎全部集中在这个“真空地带”。如何在此区间内,找到兼顾效率、体积与成本的最优解,是所有厂商都必须直面的核心难题。

技术理想也要回归工程的现实问题——成本。电源行业利润微薄的现实,决定了任何以牺牲成本为代价的性能提升都难以大规模落地。传统如增加光耦、分立的同步整流控制器、辅助绕组或缓冲电路优化思路,虽然能在一定程度上提升性能,但也会直接导致BOM膨胀、PCB布板面积紧张、生产良率下降,这一系列负面效应最终都会在成本核算环节被无情否决。

当下,电源工程师正站在关键的十字路口,呼唤着能够打破这三重枷锁的、真正具有集成与创新思维的系统级解决方案。